# HOPERF

# **CMT2218B**

## Stand-Alone Sub-1GHz G(FSK) RF Receiver

#### **Features**

■ Frequency range: 127~1020MHz

■ Demodulation: (G)FSK 和(G)MSK

■ Data rate: 0.5 ~ 300 kbps

■ Sensitivity: -121 dBm 2.0 kbps,  $F_{RF} = 433.92 \,\text{MHz}$

-111 dBm 50 kbps,  $F_{RF} = 433.92 \text{ MHz}$

■ Voltage range: 1.8 ~3.6 V

Rx current: 8.5 mA @ 433.92 MHz, FSK (High power mode)

7.2 mA @ 433.92 MHz, FSK (Low power mode)

■ Super Low Power receive mode

Sleep current: 300 nA, Duty Cycle = OFF 800 nA, Duty Cycle = ON

Receiver Features:

- Fast and stable automatic frequency control (AFC)

- 3 types of clock data recovery system (CDR)

- ◆ Fast and accurate signal detection (PJD)

- 3-wire SPI interface for EEPROM burning

- Direct mode supported

- Stand-alone working mode

- Adjustable data out 0 and 1 interval

## **Descriptions**

CMT2218B is an ultra-low power, high performance, (G) FSK RF Receiver suitable for a variety of 140 to 1020 MHz wireless applications. It is part of the CMOSTEK NextGenRFTM RF product line. The product line contains the complete transmitters, receivers and transceivers. The high integration of CMT2218B simplifies the peripheral materials required in the system design. Up to -121 dBm sensitivity optimizes the performance of the application. It supports the "antenna-in, data-out"direct mode. In addition, CMT2218B also supports GPIO and interrupt configuration, Duty-Cycle operation mode, channel sensing, high-precision RSSI, power-on reset, quelchand etc. The features make the application design more flexible and differentiated. CMT2218B operates from 1.8 V to 3.6 V. Only 8.5 mA current is consumed when the sensitivity is -121 dBm, SuperLow Power mode can further reduce the chip power consumption.

## **Applications**

- Automatic meter reading

- Home security and building automation

- ISM band data communication

- Industrial monitoring and control

- Remote control and security system

- Remote key entry

- Wireless sensor node

- Tag reader

## **Ordering information**

| Model                                       | Frequency  | Package | MOQ       |  |  |  |  |  |

|---------------------------------------------|------------|---------|-----------|--|--|--|--|--|

| CMT2218B-EQR                                | 433.92 MHz | QFN16   | 3,000 pcs |  |  |  |  |  |

| For more information, see Page 23 Table 20. |            |         |           |  |  |  |  |  |

## **Table of contents**

| 1.  | Electrical Characteristics                        | 3  |

|-----|---------------------------------------------------|----|

|     | 1.1 Recommended Operation Condition               | 3  |

|     | 1.2 Absolute Maximum Rating                       | 3  |

|     | 1.3 Power Consumption                             | 4  |

|     | 1.4 Receiver                                      | 4  |

|     | 1.5 Settle Time                                   | 6  |

|     | 1.6 Frequency Synthesizer                         | 6  |

|     | 1.7 Crystal Oscillator                            | 6  |

|     | 1.8 Low Frequency Oscillator                      |    |

|     | 1.9 Figures of Critical Parameters                |    |

|     | 1.9.1 Rx Current VS. Supply Voltage               |    |

|     | 1.9.2 Rx Current VS. Voltage Temperature          |    |

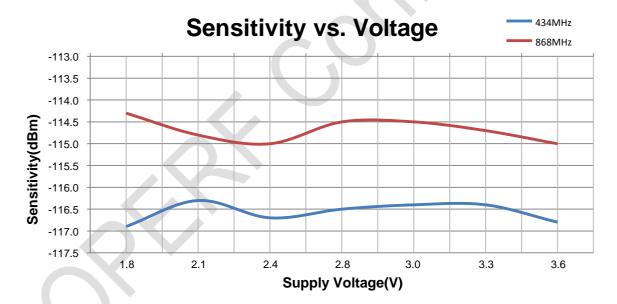

|     | 1.9.3 Sensitivity VS. Voltage                     |    |

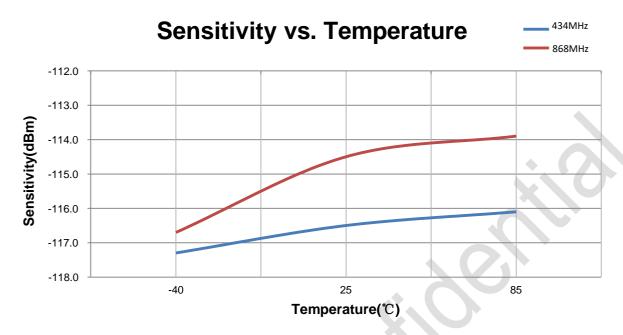

|     | 1.9.4 Sensitivity VS. Temperature                 |    |

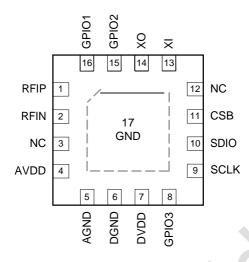

| 2   | Pin Descriptions                                  | 11 |

| 3.  | Typical Application Schematic                     | 13 |

| 4.  | Function Descriptions                             | 14 |

|     | 4.1 Receiver                                      | 14 |

|     | 4.2 Auxiliary Blocks                              |    |

|     | 4.2.1 Power-On Reset (POR)                        |    |

|     | 4.2.2 Crystal Oscillator                          |    |

|     | 4.2.3 Sleep Timer                                 |    |

|     | 4.2.4 Received Signal Strength Indicator (RSSI)   | 16 |

|     | 4.2.5 Phase Jump Detector (PJD)                   |    |

|     | 4.2.6 Automatic Frequency Control (AFC)           |    |

|     | 4.2.7 Clock Data Recovery (CDR)                   |    |

| 5.  | Chip Operation                                    | 19 |

|     | 5.1 Operation State, Timing and Power Consumption | 19 |

|     | 5.1.1 Startup Timing                              | 19 |

|     | 5.1.2 Operation State                             |    |

| 6.  | Low Power Operation                               | 21 |

|     | 6.1 Supper Low Power (SLP) Receive Mode           | 21 |

|     | 6.2 Receiver "Power VS Performance" Configuration | 21 |

| 7.  | RFPDK Configuration Interface                     | 22 |

| 8.  | Ordering Information                              | 23 |

| 9.  | Packaging Information                             | 24 |

| 10. | ). Top Marking                                    | 25 |

| 11. | l. Document Change List                           | 26 |

| 12  | 2 Contact Information                             | 27 |

## 1. Electrical Characteristics

$V_{DD}$ = 3.3 V,  $T_{OP}$ = 25 °C,  $F_{RF}$  = 433.92 MHz, the sensitivity is measured by receiving a PN9 coded data and matching the impedance to 50 $\Omega$ under the 0.1%BER standard.Unless otherwise stated, all results are tested on theCMT2218B-EM evaluation board.

## 1.1 Recommended OperationCondition

Table 1. Recommended operation condition

| Parameter             | Symbol          | Condition | Min. | Тур. | Max. | Unit       |

|-----------------------|-----------------|-----------|------|------|------|------------|

| Power voltage         | $V_{DD}$        |           | 1.8  |      | 3.6  | V          |

| Operating temperature | T <sub>OP</sub> |           | -40  |      | 85   | $^{\circ}$ |

| Power voltage slope   |                 |           | 1    |      |      | mV/us      |

## 1.2 Absolute Maximum Rating

Table 2. Absolute Maximum Ratings[1]

| Symbol          | Conditions                | Min                                                                                               | Max                                                                                                                                    | Unit                                                                                                                                                           |

|-----------------|---------------------------|---------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                 |                           |                                                                                                   |                                                                                                                                        | Ollic                                                                                                                                                          |

| $V_{DD}$        |                           | -0.3                                                                                              | 3.6                                                                                                                                    | V                                                                                                                                                              |

| $V_{\text{IN}}$ |                           | -0.3                                                                                              | V <sub>DD</sub> +0.3                                                                                                                   | V                                                                                                                                                              |

| Τ <sub>J</sub>  |                           | -40                                                                                               | 125                                                                                                                                    | $^{\circ}\!\mathbb{C}$                                                                                                                                         |

| $T_{STG}$       |                           | -50                                                                                               | 150                                                                                                                                    | $^{\circ}\!\mathbb{C}$                                                                                                                                         |

| $T_{SDR}$       | Lasts at least 30 seconds |                                                                                                   | 255                                                                                                                                    | $^{\circ}\!\mathbb{C}$                                                                                                                                         |

|                 | Human Body Model (HBM)    | -2                                                                                                | 2                                                                                                                                      | kV                                                                                                                                                             |

|                 | @ 85 ℃                    | -100                                                                                              | 100                                                                                                                                    | mA                                                                                                                                                             |

|                 | T <sub>J</sub>            | T <sub>J</sub> T <sub>STG</sub> T <sub>SDR</sub> Lasts at least 30 seconds Human Body Model (HBM) | TJ         -40           TSTG         -50           TSDR         Lasts at least 30 seconds           Human Body Model (HBM)         -2 | TJ       -40       125         TSTG       -50       150         TSDR       Lasts at least 30 seconds       255         Human Body Model (HBM)       -2       2 |

#### Notes:

[1]. Stresses above those listed as "absolute maximum ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device under these conditions is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

**Caution!** ESD sensitive device. Precaution should be used when handling the device in order to prevent permanent damage.

## 1.3 Power Consumption

Table 3. Power consumption specification

| Parameter                 | Symbol             | Condition                                      | Min. | Тур. | Max. | Unit |

|---------------------------|--------------------|------------------------------------------------|------|------|------|------|

| Classaurrant              |                    | Sleep mode, sleep timeris off                  |      | 300  |      | nA   |

| Sleepcurrent              | I <sub>SLEEP</sub> | Sleep mode, sleep timeris on                   |      | 800  |      | nA   |

| RXcurrent(high powermode) |                    | FSK, 433 MHz, 10 kbps,10 kHz F <sub>DEV</sub>  |      | 8.5  |      | mA   |

|                           | I <sub>Rx-HP</sub> | FSK, 868 MHz, 10 kbps, 10 kHz F <sub>DEV</sub> |      | 8.6  |      | mA   |

|                           |                    | FSK, 915 MHz, 10 kbps,10 kHz F <sub>DEV</sub>  |      | 8.9  |      | mA   |

|                           | I <sub>Rx-LP</sub> | FSK, 433 MHz, 10 kbps, 10 kHz F <sub>DEV</sub> |      | 7.2  |      | mA   |

| RXcurrent(low power mode) |                    | FSK, 868 MHz, 10 kbps, 10 kHz F <sub>DEV</sub> |      | 7.3  |      | mA   |

|                           |                    | FSK, 915 MHz, 10 kbps, 10 kHz F <sub>DEV</sub> |      | 7.6  |      | mA   |

## 1.4 Receiver

**Table 4. Receiver specification**

| Parameter               | Symbol              | Condition                                                                              | Min. | Тур. | Max. | Unit  |

|-------------------------|---------------------|----------------------------------------------------------------------------------------|------|------|------|-------|

| Data rate               | DR                  | FSK and GFSK                                                                           | 0.5  |      | 300  | kbps  |

| Deviation               | $F_{DEV}$           | FSK and GFSK                                                                           | 2    |      | 200  | kHz   |

|                         |                     | $DR = 2.0 \text{ kbps}, F_{DEV} = 10 \text{ kHz}$                                      |      | -121 |      | dBm   |

|                         |                     | $DR = 10 \text{ kbps}, F_{DEV} = 10 \text{ kHz}$                                       |      | -116 |      | dBm   |

|                         |                     | DR = 10 kbps, $F_{DEV}$ = 10 kHz (Low power setting)                                   |      | -115 |      | dBm   |

|                         |                     | $DR = 20 \text{ kbps}, F_{DEV} = 20 \text{ kHz}$                                       |      | -113 |      | dBm   |

| Sensitivity             | S <sub>433-HP</sub> | DR = 20 kbps, $F_{DEV}$ = 20 kHz (Low power                                            |      |      |      | dBm   |

| @ 433 MHz               | <b>433-11</b>       | setting)                                                                               |      | -112 |      |       |

|                         |                     | DR = 50 kbps, $F_{DEV}$ = 25 kHz                                                       |      | -111 |      | dBm   |

|                         |                     | DR =100 kbps, F <sub>DEV</sub> = 50 kHz                                                |      | -108 |      | dBm   |

|                         |                     | DR =200 kbps, F <sub>DEV</sub> = 100 kHz                                               |      | -105 |      | dBm   |

|                         |                     | DR =300 kbps, F <sub>DEV</sub> = 100 kHz                                               |      | 103  |      | dBm   |

|                         |                     | $DR = 2.0 \text{ kbps}, F_{DEV} = 10 \text{ kHz}$                                      |      | -119 |      | dBm   |

|                         |                     | $DR = 10 \text{ kbps}, F_{DEV} = 10 \text{ kHz}$                                       |      | -113 |      | dBm   |

|                         |                     | DR = 10 kbps, $F_{DEV}$ = 10 kHz (Low powersetting)                                    |      | -111 |      | dBm   |

|                         |                     | $DR = 20 \text{ kbps}, F_{DEV} = 20 \text{ kHz}$                                       |      | -111 |      | dBm   |

| Sensitivity  @ 868 MHz  | S <sub>868-HP</sub> | DR = 20 kbps, F <sub>DEV</sub> = 20 kHz (Low power setting)                            |      | -109 |      | dBm   |

|                         |                     | DR = 50 kbps, F <sub>DEV</sub> = 25 kHz                                                |      | -108 |      | dBm   |

|                         |                     | DR =100 kbps, F <sub>DEV</sub> = 50 kHz                                                |      | -105 |      | dBm   |

|                         |                     | DR =200 kbps, F <sub>DEV</sub> = 100 kHz                                               |      | -102 |      | dBm   |

|                         |                     | DR =300 kbps, F <sub>DEV</sub> = 100 kHz                                               |      | -99  |      | dBm   |

|                         |                     | DR = 2.0 kbps, F <sub>DEV</sub> = 10 kHz                                               |      | -117 |      | dBm   |

|                         |                     | DR = 10 kbps, F <sub>DEV</sub> = 10 kHz                                                |      | -113 |      | dBm   |

| Sensitivity             | S <sub>915-HP</sub> | DR = 10 kbps, F <sub>DEV</sub> = 10 kHz (Low power mode)                               |      | -111 |      | dBm   |

| @ 915 MHz               | O915-HP             | DR = 20 kbps, $F_{DEV}$ = 20 kHz                                                       |      | -111 |      | dBm   |

|                         |                     | DR = 20 kbps, $F_{DEV}$ = 20 kHz (Low power mode)                                      |      | -109 |      | dBm   |

|                         |                     | DR = 50 kbps, $F_{DEV}$ = 25 kHz                                                       |      | -109 |      | dBm   |

|                         |                     | DR =100 kbps, F <sub>DEV</sub> = 50 kHz                                                |      | -105 |      | dBm   |

|                         |                     | DR =200 kbps, F <sub>DEV</sub> = 100 kHz                                               |      | -102 |      | dBm   |

|                         |                     | DR =300 kbps, F <sub>DEV</sub> = 100 kHz                                               |      | 99   |      | dBm   |

| Saturation Input Signal |                     | DIV = 000 KBp0, I DEV = 100 KI IZ                                                      |      |      |      | abili |

| Level                   | P <sub>LVL</sub>    |                                                                                        |      |      | 20   | dBm   |

|                         |                     | F <sub>RF</sub> =433 MHz                                                               |      | 35   |      | dB    |

| Image Rejection Ratio   | IMR                 | F <sub>RF</sub> =868 MHz                                                               |      | 33   |      | dB    |

|                         |                     | F <sub>RF</sub> =915 MHz                                                               |      | 33   |      | dB    |

| RX Channel<br>Bandwidth | BW                  | RX channel bandwidth                                                                   | 50   |      | 500  | kHz   |

| Co-channel Rejection    |                     | DR = 10 kbps, F <sub>DEV</sub> = 10 kHz; Interference with                             |      | _    | 1    |       |

| Ratio                   | CCR                 | the same modulation                                                                    |      | -7   |      | dB    |

|                         |                     | $DR = 10 \text{ kbps}, F_{DEV} = 10 \text{ kHz}; BW = 100 \text{kHz}, 200$             |      |      |      |       |

| Adjacent Channel        | ACR-I               | kHzChannel spacing, interference with the same                                         |      | 30   |      | dB    |

| Rejection Ratio         |                     | modulation                                                                             |      |      |      |       |

| Alta cara Cl            |                     | DR = 10 kbps, $F_{DEV}$ = 10 kHz; BW=100kHz, 400                                       |      |      |      |       |

| AlternateChannel        | ACR-II              | kHzChannel spacing, interference with the same                                         |      | 45   |      | dB    |

| Rejection Ratio         |                     | modulation                                                                             |      |      |      |       |

|                         |                     | DR = 10 kbps, F <sub>DEV</sub> = 10 kHz; ±1 MHzDeviation, continuous wave interference |      | 70   |      | dB    |

| Blocking Rejection      | ы                   | DR = 10 kbps, $F_{DEV}$ = 10 kHz; ± 2 MHzDeviation,                                    |      | 70   |      | J.C   |

|                         | BI                  | continuous wave interference                                                           |      | 72   |      | dB    |

## CMT2218B

| Ratio                                          |      | DR = 10 kbps, F <sub>DEV</sub> = 10 kHz; ±10 MHzDeviation, continuous wave interference                         |      | 75     |    | dB  |

|------------------------------------------------|------|-----------------------------------------------------------------------------------------------------------------|------|--------|----|-----|

| Input 3 <sup>rd</sup> Order<br>Intercept Point | IIP3 | DR = 10 kbps, F <sub>DEV</sub> = 10 kHz; 1 MHz and 2 MHz Deviation dual tone test, maximum system gain setting. |      | -25    |    | dBm |

| RSSI Range                                     | RSSI |                                                                                                                 | -120 |        | 20 | dBm |

|                                                |      | 433.92 MHz, DR = 1.2kbps, F <sub>DEV</sub> = 5 kHz                                                              |      | -122.9 |    | dBm |

|                                                |      | 433.92 MHz, DR = 1.2kbps, F <sub>DEV</sub> = 10 kHz                                                             |      | -121.8 |    | dBm |

|                                                |      | 433.92 MHz, DR = 1.2kbps, F <sub>DEV</sub> = 20 kHz                                                             |      | -119.5 |    | dBm |

|                                                |      | 433.92 MHz, DR = 2.4kbps, F <sub>DEV</sub> = 5 kHz                                                              |      | -120.6 |    | dBm |

|                                                |      | 433.92 MHz, DR = 2.4kbps, F <sub>DEV</sub> = 10 kHz                                                             |      | -120.3 |    | dBm |

|                                                |      | 433.92 MHz, DR = 2.4kbps, F <sub>DEV</sub> = 20 kHz                                                             |      | -119.7 |    | dBm |

|                                                |      | 433.92 MHz, DR = 9.6 kbps, F <sub>DEV</sub> = 9.6 kHz                                                           |      | -116.0 |    | dBm |

|                                                |      | 433.92 MHz, DR = 9.6 kbps, FDEV = 19.2 kHz                                                                      |      | -116.1 |    | dBm |

| More Sensitivity (Typical Configuration)       |      | 433.92 MHz, DR = 20 kbps, FDEV = 10 kHz                                                                         | 4    | -114.2 |    | dBm |

| (Typical Colliguration)                        |      | 433.92 MHz, DR = 20 kbps, FDEV = 20 kHz                                                                         |      | -113.0 |    | dBm |

|                                                |      | 433.92 MHz, DR = 50 kbps, FDEV = 25 kHz                                                                         | X    | -110.6 |    | dBm |

|                                                |      | 433.92 MHz, DR = 50 kbps, FDEV = 50 kHz                                                                         |      | -109.0 |    | dBm |

|                                                |      | 433.92 MHz, DR = 100 kbps, FDEV = 50 kHz                                                                        |      | -107.8 |    | dBm |

|                                                |      | 433.92 MHz, DR = 200 kbps, FDEV = 50 kHz                                                                        |      | -103.5 |    | dBm |

|                                                |      | 433.92 MHz, DR = 200 kbps, FDEV = 100 kHz                                                                       |      | -104.3 |    | dBm |

|                                                |      | 433.92 MHz, DR = 300 kbps, FDEV = 50 kHz                                                                        |      | -98.0  |    | dBm |

|                                                |      | 433.92 MHz, DR = 300 kbps, FDEV = 150 kHz                                                                       |      | -101.6 |    | dBm |

## 1.5 SettleTime

Table 5. SettleTime

| Parameter                                      | Symbol              | Condition                                     | Min.        | Тур.         | Max. | Unit |

|------------------------------------------------|---------------------|-----------------------------------------------|-------------|--------------|------|------|

| Settle time                                    | T <sub>SLP-RX</sub> | From Sleep to RX                              |             | 1000         |      | us   |

| Note: [1]. T <sub>SLP-RX</sub> is dominated by | the crystal         | oscillator startup time, which depends on its | s own chara | acteristics. |      |      |

## 1.6 Frequency Synthesizer

**Table 6. Frequency Synthesizer Specifications**

| Parameter             | Symbol            | Condition                        | Min. | Тур. | Max. | Unit   |

|-----------------------|-------------------|----------------------------------|------|------|------|--------|

|                       |                   |                                  | 760  |      | 1020 | MHz    |

|                       |                   | Need different matching networks | 380  |      | 510  | MHz    |

| Frequency range       | F <sub>RF</sub>   |                                  | 190  |      | 340  | MHz    |

|                       |                   | C                                | 127  |      | 170  | MHz    |

| Frequency resolution  | F <sub>RES</sub>  |                                  |      | 25   |      | Hz     |

| Frequency tuning time | t <sub>TUNE</sub> |                                  |      | 150  |      | us     |

|                       |                   | 10 kHz frequency deviation       |      | -94  |      | dBc/Hz |

| <b>5</b> 1 0 100      | PN <sub>433</sub> | 100 kHz frequency deviation      |      | -99  |      | dBc/Hz |

| Phase noise@ 433      |                   | 500 kHz frequency deviation      |      | -118 |      | dBc/Hz |

| MHz                   |                   | 1MHz frequency deviation         |      | -127 |      | dBc/Hz |

|                       |                   | 10 MHz frequency deviation       |      | -134 |      | dBc/Hz |

|                       |                   | 10 kHz frequency deviation       |      | -92  |      | dBc/Hz |

| <b>5</b> 1            |                   | 100 kHz frequency deviation      |      | 95   |      | dBc/Hz |

| Phase noise@ 868      | PN <sub>868</sub> | 500 kHz frequency deviation      |      | -114 |      | dBc/Hz |

| MHz                   |                   | 1MHz frequency deviation         |      | -121 |      | dBc/Hz |

|                       |                   | 10 MHz frequency deviation       |      | -130 |      | dBc/Hz |

|                       |                   | 10 kHz frequency deviation       |      | -89  |      | dBc/Hz |

|                       |                   | 100 kHz frequency deviation      |      | -92  |      | dBc/Hz |

| Phase noise@ 915      | PN <sub>915</sub> | 500 kHz frequency deviation      |      | -111 |      | dBc/Hz |

| MHz                   |                   | 1MHz frequency deviation         |      | -121 |      | dBc/Hz |

|                       |                   | 10 MHz frequency deviation       |      | -130 |      | dBc/Hz |

## 1.7 Crystal Oscillator

**Table 7. Crystal Oscillator Specifications**

| Parameter                          | Symbol            | Condition | Min. | Тур. | Max. | Unit |  |  |

|------------------------------------|-------------------|-----------|------|------|------|------|--|--|

| Crystal frequency <sup>[1]</sup>   | F <sub>XTAL</sub> |           |      | 26   |      | MHz  |  |  |

| Frequency tolerance <sup>[2]</sup> | ppm               |           |      | 20   |      | ppm  |  |  |

| Load capacitance                   | C <sub>LOAD</sub> |           |      | 15   |      | pF   |  |  |

| Equivalent resistance              | Rm                |           |      | 60   |      | Ω    |  |  |

| Start-up time <sup>[3]</sup>       | t <sub>XTAL</sub> |           |      | 400  |      | us   |  |  |

| Remarks:                           |                   |           |      |      |      |      |  |  |

- [1]. CMT2218B can use the external reference clock to drive the XIN pin through the coupling capacitor. The peak value of the external clock signal is between 0.3V and 0.7V.

- [2]. The value includes (1) initial error; (2) crystal load; (3) aging; and (4) change with temperature. The acceptable crystal frequency tolerance is limited by the receiver bandwidth and the RF frequency offset between the transmitter and the receiver.

- [3]. The parameter is largely related to the crystal.

## 1.8 Low Frequency Oscillator

**Table 8. Low Frequency Oscillator Specifications**

| Parameter                      | Symbol                 | Condition         | Min. | Тур.  | Max. | Unit |

|--------------------------------|------------------------|-------------------|------|-------|------|------|

| Calibration frequency [1]      | F <sub>LPOSC</sub>     |                   |      | 32    |      | kHz  |

| Frequency accuracy             |                        | After calibration |      | ±1    |      | %    |

| Temperature coefficient [2]    |                        |                   |      | -0.02 |      | %/°C |

| Supply voltage coefficient [3] |                        |                   |      | +0.5  |      | %/V  |

| Initial calibration time       | t <sub>LPOSC-CAL</sub> |                   |      | 4     |      | ms   |

#### Remarks:

- [1]. The low frequency oscillator is automatically calibrated to the crystal oscillator frequency at the PUP stage and periodically calibrated at this stage.

- [2]. After calibration, the frequency changes with temperature.

- [3]. After calibration, the frequency changes with the change of the supply voltage.

## 1.9 Figures of Critical Parameters

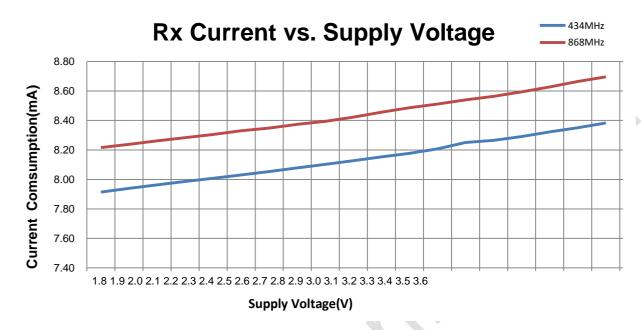

### 1.9.1 Rx Current VS. Supply Voltage

Testing Condition: Freq = 434MHz / 868MHz, Fdev = 10KHz, BR = 10Kbps

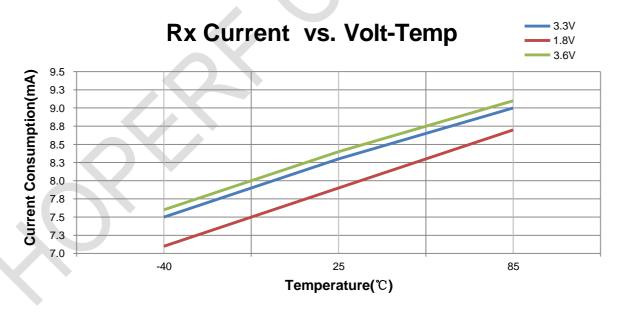

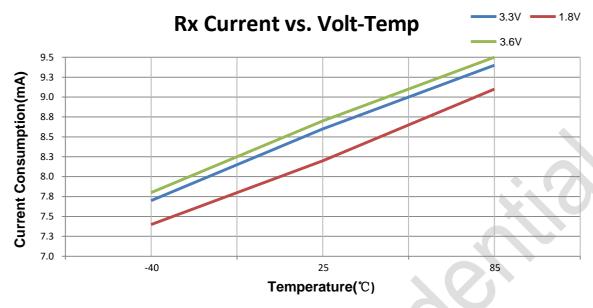

### 1.9.2 Rx Current VS. Voltage Temperature

Test Condition: Freq = 434MHz,Fdev = 10KHz, BR = 10Kbps

Test Condition: Freq = 868MHz, Fdev = 10KHz, BR = 10Kbps

### 1.9.3 Sensitivity VS. Voltage

Test Condition: FSK, DEV = 10KHz, BR = 10Kbps

## 1.9.4 Sensitivity VS. Temperature

Test Condition: FSK, DEV = 10KHz, BR = 10Kbps

## 2. Pin Descriptions

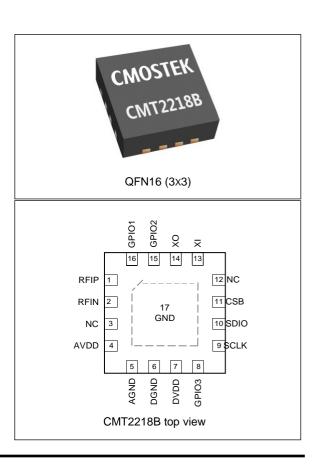

Figure 1. CMT2218B pin arrangements

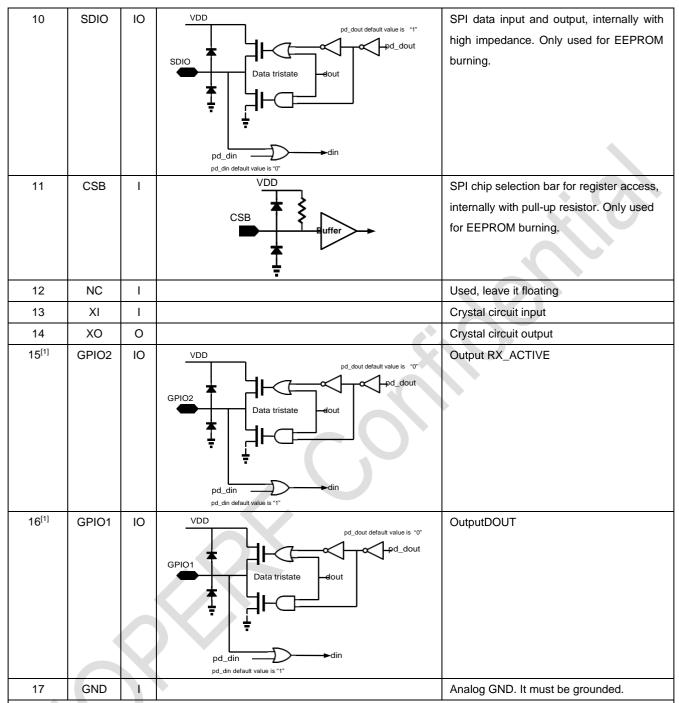

Table 9. CMT2218B pin descriptions

| Pin No. | Name  | I/O | Internal IO Schematic                                              | Descriptions                                                                 |

|---------|-------|-----|--------------------------------------------------------------------|------------------------------------------------------------------------------|

| 1       | RFIP  | ı   |                                                                    | RF signal input P                                                            |

| 2       | RFIN  | I   |                                                                    | RF signal input N                                                            |

| 3       | PA    | 0   |                                                                    | Used, leave it floating                                                      |

| 4       | AVDD  | Ю   |                                                                    | Analog VDD                                                                   |

| 5       | AGND  | Ю   |                                                                    | Analog GND                                                                   |

| 6       | DGND  | Ю   |                                                                    | Digital GND                                                                  |

| 7       | DVDD  | Ю   |                                                                    | Digital VDD                                                                  |

| 8[1]    | GPIO3 | Ю   | pd_dout default value is "0"  pd_dout default value is "0"  pd_din | Configured as DOUT, RX_ACTIVE, DCLK                                          |

| 9       | SCLK  | I   | SCLK Buffer din                                                    | SPI clock, internally with pull-down resistor. Only used for EEPROM burning. |

#### Note:

- [1]. GPIO1, output DOUT: in Rx state, it outputs continues demodulated data; in other state, it outputs logic 0.

- GPIO2, output RX\_ACTIVE: it goes high at about 350 us before entering the Rx state, and goes low when exiting Rx state. GPIO3, options: DOUT, RX\_ACTIVE and DCLK. DCLK is the data rate clock synchronized to the demodulated data, used for the MCU to capture and decode the data.

- [2]. SDIO has internal high impedance. User must add 10K pull-up resistor outside the chip to avoid possible leakage current.

## 3. Typical Application Schematic

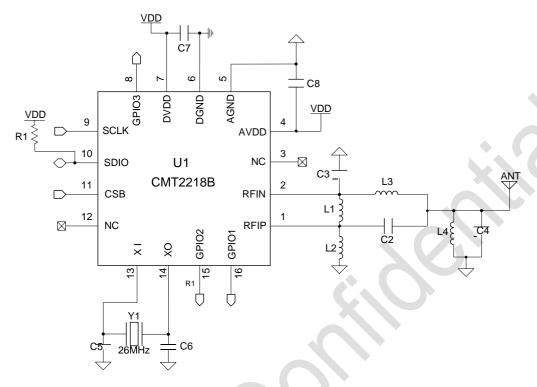

Figure 2. Application schematic diagram

**Table 10. Application BOM**

|     | Descriptions                             | Value   |         |         |       |              |

|-----|------------------------------------------|---------|---------|---------|-------|--------------|

| No. |                                          | 433 MHz | 868 MHz | 915 MHz | Unit  | Supplier     |

| R1  | ±5%, 0603,                               |         | 10      |         | ΚΩ    |              |

| C2  | ±5%, 0603 NP0, 50 V                      | 4.7     | 2.2     | 2.2     | pF    |              |

| C3  | ±5%, 0603 NP0, 50 V                      | 4.7     | 2.2     | 2.2     | pF    |              |

| C4  | ±5%, 0603 NP0, 50 V                      | 4.7     | 2.2     | 2.2     | pF    |              |

| C5  | ±5%, 0603 NP0, 50 V                      | 24      |         | pF      |       |              |

| C6  | ±5%, 0603 NP0, 50 V                      | 24      |         | pF      |       |              |

| C7  | ±5%, 0603 NP0, 50 V                      | 470     |         | pF      |       |              |

| C8  | ±5%, 0603 NP0, 50 V                      | 0.1     |         | uF      |       |              |

| L1  | ±5%, 0603 Multilayer chip inductor       | 68      | 12      | 12      | nH    | Sunlord SDCL |

| L2  | ±5%, 0603 Multilayer chip inductor       | 27      | 15      | 12      | nH    | Sunlord SDCL |

| L3  | ±5%, 0603 Multilayer chip inductor       | 27      | 15      | 12      | nH    | Sunlord SDCL |

| L4  | ±5%, 0603 Multilayer chip inductor       | 27      | 15      | 12      | nH    | Sunlord SDCL |

| Y1  | ±10 ppm, SMD32*25 mm                     | 26      |         | MHz     | EPSON |              |

| U1  | CMT2218B,Stand-Alone Sub-1GHzRF Receiver |         |         |         | -     | CMOSTEK      |

## 4. Function Descriptions

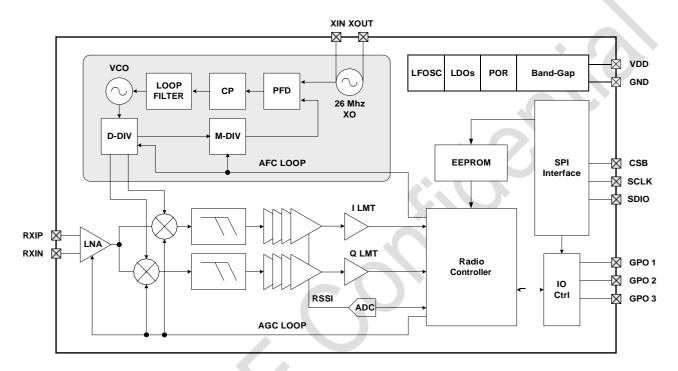

CMT2218B is an ultra-low power, high performancereceiver chip. It uses a 26 MHz crystal oscillator as a reference clock for the internal PLL. It supports (G) FSK and (G) MSK, as well as stand-alone work mode without the need of being controlled by external MCU. It also supports various duty-cycle mode to reduce the current consumption and increase the stability. It is suitable for applications ranging from 140 to 1020MHz. The demodulated data is sent out directly from GPO. CMT2218B block diagramis as shown in the following figure.

Figure 3. Functional Block Diagram

In the receiver part, the chip uses LNA+MIXER+IFFILTER+LIMITTER+PLL low-IF architecture to achieve the Sub-GHz wireless reception function.

In the receiver system, the analog circuit mixes the RF signal to IF and converts the signal from analog to digital through the Limiter module, then outputs I/Q two single bit signals to the digital circuit for (G) FSK demodulation. At the same time, SARADC will convert the real-time RSSI signal to 8-bit digital signal, and sent them to the digital part for the other processing. The digital circuit is responsible for mixing the intermediate frequency to zero frequency (Baseband) and performing a series of filtering and decision processing, while AFC and AGC control the analog circuit dynamically, finally the 1-bit original signal is demodulated and sent to the GPO directly.

The chip provides the SPI communication port for burning the EEPROM. Users need to use the tools provided by CMOSTEK.

#### 4.1 Receiver

CMT2218B has a built-in ultra-low power, high performance low-IF FSK receiver. The RF signal induced by the antennais amplified by a low noise amplifier, and is converted to an intermediate frequency by an orthogonal mixer. The signal is filtered by the image rejection filter, and is amplified by the limiting amplifier and then sent to the digital domain for digital demodulation. During power on reset (POR) each analog block is calibrated to the internal reference voltage. This allows the chip to remain its best performance at different temperatures and voltages. Baseband filtering and demodulation isdone by the digital demodulator. The AGC loop adjust the system gain by the broadband power detector and attenuation network nearby LNA, so as

to obtain the best system linearity, selectivity, sensitivity and other performance.

LeveragingCMOSTEK's low power design technology, the receiver consumes only a very low power when it is turned on. The periodic operation mode and wake up function can further reduce the average power consumption of the system in the application with strict requirements of power consumption.

### 4.2 Auxiliary Blocks

#### 4.2.1 Power-On Reset (POR)

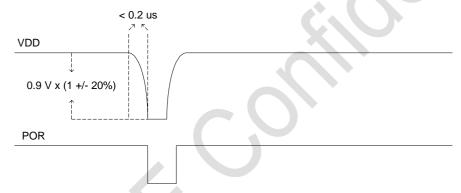

The Power-On Reset circuit detect the change of the VDD power supply, and generate the reset signal for the entire CMT2218B system. After the POR, the MCU must go through the initialization process and re-configure the CMT2218B. There are two circumstances those will lead to the generation of POR.

The first case is a very short and sudden decrease of VDD. The POR triggering condition is, VDD dramatically decreases by 0.9V +/- 20% (e.g. 0.72V – 1.08V) within less than 2 us. To be noticed, it detects a decreasing amplitude of the VDD, not the absolute value of VDD.

Figure 4. Sudden Decrease of VDD lead to Generation of POR

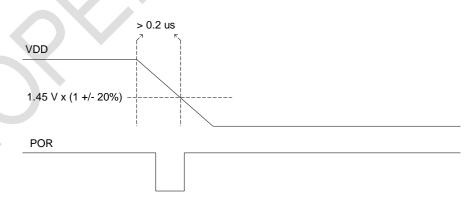

The second case is, a slow decrease of the VDD. The POR triggering condition is, VDD decreases to 1.45V + /-20% (e.g. 1.16V - 1.74V) within a time more than or equal to 2 us. To be noticed, it detects an absolute value of VDD, not a decreasing amplitude.

Figure 5. Slow Decrease of VDD lead to Generation of POR

#### 4.2.2 Crystal Oscillator

The crystal oscillator provides a reference clock for the phase locked loop as well as a system clock for the digital circuits. The value of load capacitance depends on the crystal specified CL parameters. The total load capacitance between XI and XO should be equal to CL, in order to make the crystal accurately oscillate at 26 MHz.

C15 and C16 are the load capacitancesat both ends of the crystal. Cpar is the parasitic capacitance on the PCB. Each crystal pin has 5pF internal parasitic capacitance, together is equivalent to 2.5pF. The equivalent series resistance of the crystal must be within the specifications so that the crystal can have a reliable vibration. Also, an external signal source can be connected to the XI pin to replace the conventional crystal. The recommended peak value of this clock signal is from 300mV to 700mV. The clock is coupled to XI pin via a blocking capacitor.

#### 4.2.3 Sleep Timer

The CMT2218B integrates a sleep timer driven by 32 kHz low power oscillator (LPOSC). When this function is enabled, the timer wakes the chip from sleep periodically. When the chip operates in a duty cycle mode, the sleep time can be configured from 0.03125 ms to 41922560 ms. Due to the low power oscillator frequency will change with the temperature and voltage drift, it will be automatically calibrated during power on and will be periodically calibrated since then. These calibrations will keep the frequency tolerance of the oscillator within + 1%.

#### 4.2.4 Received Signal Strength Indicator(RSSI)

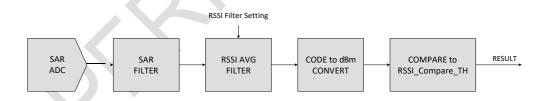

RSSI is used to evaluate the signal strengthinside the channel. The cascaded I/Q logarithmic amplifier amplifies the signal before it is sent to the demodulator. The logarithmic amplifier of I channels and Q channel contains the received signal indicator, in which the DC voltage is generated is proportional to the input signal strength. The output of RSSI is the sum of thevalues of the two channels' signals. The output has 80dB dynamic range above the sensitivity. After the RSSI output is sampled by the ADC and filtered by a SAR FILTER and a RSSI AVG FILTER. The order of the average filter can be set by RSSI Filter Setting on RFPDK. The code value is translated into dBm value after filtering and compare with the RSSI\_Compare\_TH. If the RSSI is larger than the threshold it outputs logic 1, otherwise outputs logic 0. The output can be used as the receive time extending condition in the super low power (SLP) mode.

Figure 6. RSSI detection and comparison circuit

CMT2218B has done a certain degree of calibration before delivery. In order to obtain more accurate RSSI measurement results, the user needs to recalibrate the RSSI circuit in their dedicated applications. For further information, please refer to the "AN181-CMT2218BW RSSI Usage Guideline".

#### 4.2.5 Phase Jump Detector (PJD)

PJD is Phase Jump Detector. When the chip is in FSK demodulation, it automatically observe the phase jump characteristics of the received signal to determine whether it is awanted signal or an unwanted noise.

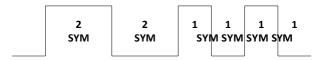

Figure 7. Received signal jump diagram

The PJD mechanism defines that the input signal switching from 0 to 1 or from 1 to 0 is a phase jump. Users can configure the PJD Window to determine the number of detected jumps for the PJD to identify a wanted signal. As shown in the above figure, in total 8 symbols are received. But the phase jump only appeared 6 times. Therefore, the number of jumpsis not equal to the number of symbols. Only when a preamble is received theyare equal. In general, the more jumps are used to identify the signal, the more reliable they result is; the less jumps are used, the faster the result is obtained. If the RX time is set to a relatively short period, it is necessary to reduce the number of jumps to meet the timing requirements. Normally, 4 jumps allow pretty reliable result, e.g. the chip will not mistakenly treat an incoming noise as a wanted signal, and vice versa will not treat a wanted signal as noise.

Detecting the phase jump of a signal, is identical to detect whether the signal has the expecteddata rate. In fact, at the same time, the PJD will also detect the FSK deviation and see if it is legal, as well as to see if the SNR is over 7 dB. With these three parameters the PJD is able to make a very reliable judgement. If the signal is wanted it outputs logic 1, otherwise outputs logic 0. The output can be used as a source of the RSSI VLD interrupt, or the receive time extending condition in the super low power (SLP) mode. In direct data mode, by enabling the Dout Mute, the PJD can mute the FSK demodulated data output while there is not wanted signal received.

The PJD technique is similar to the traditional carrier sense technique, but more reliable. While users combine the RSSI detection and PJD technique, they can precisely identify the status of the current channel.

#### 4.2.6 Automatic Frequency Control (AFC)

The AFC mechanism allows the receiver to minimize the frequency error between the TX and RX in a very short time once a wanted signal comes in. This helps the receiver to maintain its highest sensitivity performance. CMT2218B has the most advanced AFC technology. Compare with the other competitors, within the same bandwidth, CMT2218B can identify larger frequency error, and remove the error in a much shorter time (8-10 symbols).

Normally the frequency error between the TX and RX is caused by the crystal oscillators used in both sides. CMT2218B allows the user to fill in the value of crystal tolerance (in PPM) on RFPDK. Based on the crystal tolerance, the RFPDK will calculate the AFC range whileminimizing the receiver bandwidth (to maintain the best performance). Due to the excellent performance of the AFC, it provides a good solution to the crystal aging problem which would lead to more frequency error as time goes by. Therefore, compare to other similar receiver chips, CMT2218B can solve more severe crystal aging problem and effectively extend the life time of the product.

#### 4.2.7 Clock Data Recovery (CDR)

The basic task of a CDR system is to recover the clock signal that is synchronized with the symbol rate, while receiving the data. Not only for processing the data inside the chip, but also for outputting the synchronized clock to GPIO for users to sample the data. So CDR's task is simple and important. If the recovered clock frequency is in error with the actual symbol rate, it will cause data acquisition errors at the time of reception.

CMT2218BW has designed three types of CDR systems, as follows:

- 1. **COUNTING system**—The system is designed for the symbol rates to be more accurate. If the symbol rate is 100% aligned, the unlimited length of 0 can be received continuously without error.

- 2. **TRACING system** –The system is designed to correctthe symbol rate error. It has the tracking function. It can automatically detect the symbol rate transmitted by TX, and adjust quickly the local symbol rate of RX at the same time, so as to minimize the error between them. The system can withstand up to 15.6% or symbol rate error. Other similar products in the industry cannot reach this level.

- 3. **MANCHESTER system** –This system evolves from the COUNTING system. The basic feature is the same. The only difference is that the system is specially designed for Manchester codec. Special processing can be done when the TX symbol rate has unexpected changes.

## 5. ChipOperation

### 5.1 Operation State, Timing and Power Consumption

#### 5.1.1 Startup Timing

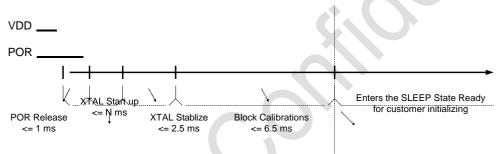

After the chip VDD is powered up, the chip usually needs to wait about 1ms, then POR will release. After the release of the POR, the crystal will start, the start time is 200 us - 1 ms, depending on the characteristics of the crystal itself. After starting, the user need to wait for the crystal settled, then the system starts working. The default setting is 2.48ms. This time can be modified by writing XTAL Stable Time afterword (it has to be longer than the crystal inherent settling time). However, if the inherent settling time of the crystal is difficult to observed by the user, the default setting of 2.48 ms is recommended and is able to cover most of the crystals.

The chip remains in the IDLE status until the crystal is settled. After the crystal is settled, the chip will leave the IDLE state and begin to do the calibration of each module. After the calibration is completed, the chip will enter the duty-cycle working mode, or always stay in the Rx state until power down.

Figure 8. Power on sequence

#### 5.1.2 OperationState

CMT2218B has 2operationstates: SLEEP and RX.

#### ■ SLEEP State

The chip power consumption is the lowest in SLEEP state, and almost all the modules are turned off. The time required to switch from IDLE to SLEEP is the power up time. Switch from other state to SLEEP will be completed immediately.

#### RX State

All modules on the receiver will be opened in RX state. Switching from SLEEP to RX needs to add the crystal start-up and settled time.

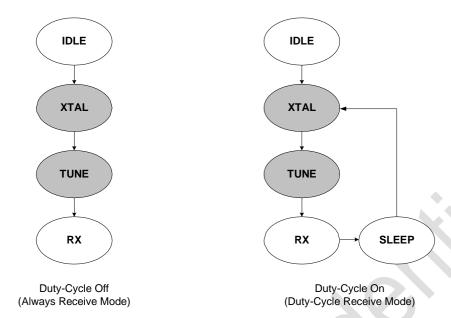

After the internal EEPROM of CMT2218B is successfully burned, the chip will enter the receive mode after power up. There are 2 receive modes available. One is the Always Receive Mode which turns off the duty-cycle operation. Another is the duty-cycle receive mode, which constantly switches the state between RX and SLEEP according to the user's configurations, as well as supports the Super Low Power (SLP) control mechanism.

Figure 9. CMT2218B State Switch Diagram

The XTAL and TUNE in the figure are not specific states, but processes. XTAL stands for the process of crystal oscillator starting up and stabilizing. TUNE stands for the process of PLL locking and frequency tuning, taking about 350 us to complete. The RX and SLEEP time are configured on the RFPDK by the users. To be noticed, if the chip works in the duty-cycle receive mode, each time it wakes up from SLEEP, it will wait for the crystal oscillator to start up and get stable before entering the RX state.

## 6. Low Power Operation

### 6.1 Supper Low Power (SLP) Receive Mode

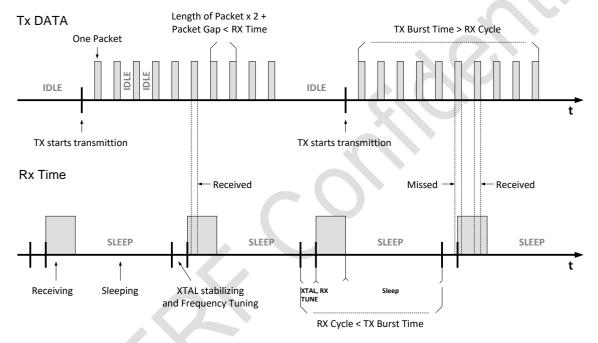

CMT2218B provides a set of options to help users achieve supper low power consumption (SLP - Supper Low Power) reception under different application requirements. These options can be used in the duty-cycle receive mode. The principle of the SLP mechanism is to shorten the Rx time when there is no wanted signal coming in, and properly extend the Rx time when there is wanted signal detected, so that the power consumption is minimized while the stability of reception is guaranteed. The traditional short-range wireless receiver generally uses the following basic scheme to achieve low powercommunication. CMT2218B is also compatible with this scheme, and expands it to 2 more power-saving schemes. The figure below introduces the most basic scheme, which can be realized by the normal duty-cycle receive mode, as well as the two super-low-power schemes extended from the basic one.

Figure 10. Basic low-power receiver scheme

| No. | Rx Extended Methods                                                                                   | Rx Extended Condition |

|-----|-------------------------------------------------------------------------------------------------------|-----------------------|

| 4   | Once detect RSSI_VLD = 1 during T1, leave T1 and stays in Rx state, exit Rx state until RSSI_VLD = 0. | RSSI_VLD is valid.    |

| 5   | Once meet the Rx extended condition during T1, switch to T2. Exit Rx as soon as T2 timed out.         | RSSI_VLD is valid     |

Table 11. Low-power receiver mode

The T1 and T2 mentioned in the table refer to the RX T1 and the RX T2 time interval that can be set via the registers or RFPDK. The source of RSSI\_VLD can be the comparison result of the RSSI or the detection result of the phase jump detector (PJD). For more details, please refer to "AN179-CMT2218BW Low Power Mode Usage Guideline".

### 6.2 Receiver "Power VS Performance" Configuration

CMT2218B provides a set of registers to select the power consumption and sensitivity performance of the RF frontend circuit. The higher the performance is set, the higher the current is consumed.

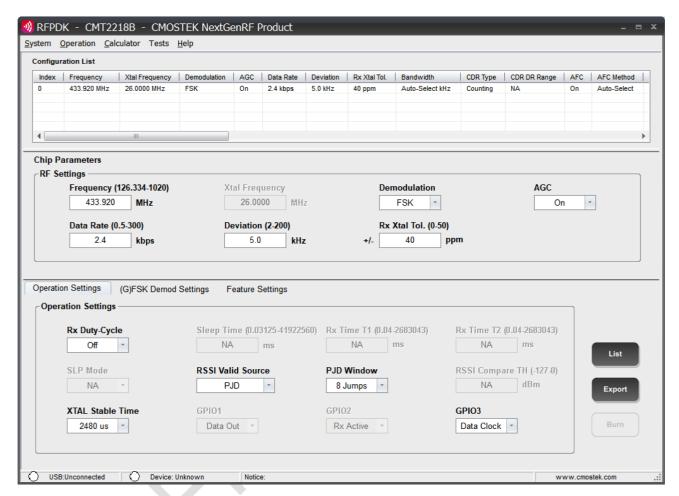

## 7. RFPDK Configuration Interface

RFPDK is a Windows based software tool provided by CMOSTEK for configuring the RF products. For CMT2218B, the user can configure the chip by filling all the parameters on the interface, then burn the EEPROM inside the chip using the CMOSTEK programmer.

Figure 11. RFPDK configuration interface

## 8. Ordering Information

Table12. CMT2218B ordering information

| Part Number                  | Descriptions                   | Packaging   | Packing        | Condition    | MOQ   |

|------------------------------|--------------------------------|-------------|----------------|--------------|-------|

| CMT2218B-EQR <sup>[1]</sup>  | CMT2218B, Stand-Alone Sub-1GHz | OEN46 (2v2) | x3) Tape& Reel | 1.8 to 3.6V, | 3,000 |

| CW112218B-EQR <sup>113</sup> | (G)FSK RF receiver             | QFN16 (3x3) |                | -40 to 85℃   |       |

#### Note:

- [1]. "E" represents extended industrial grade. The temperature range is from -40 to +85.

- "Q" represents QFN16 packaging.

- "R" represents tape &reel packing. MOQ is 3000pcs.

For more information about product, please visitwww.hoperf.com.

For purchasing or price requirements, please contactsales@hoperf.com\_or local sales representative.

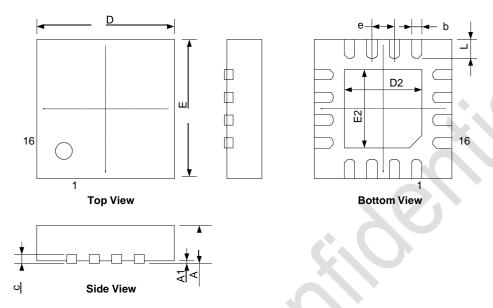

## 9. Packaging Information

CMT2218B packaging is QFN16 (3x3). The packaging information is as below.

Figure 12. 16-Pin QFN 3x3 packaging

Table13. 16-Pin QFN 3x3 Packaging Size

|        | Size (mm) |      |  |

|--------|-----------|------|--|

| Symbol | Min.      | Max. |  |

| А      | 0.7       | 0.8  |  |

| A1     | _         | 0.05 |  |

| b      | 0.18      | 0.30 |  |

| С      | 0.18      | 0.25 |  |

| D      | 2.90      | 3.10 |  |

| D2     | 1.55      | 1.75 |  |

| е      | 0.50 BSC  |      |  |

| E      | 2.90      | 3.10 |  |

| E2     | 1.55      | 1.75 |  |

| L      | 0.35      | 0.45 |  |

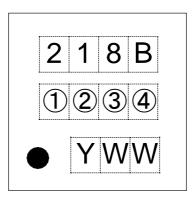

## 10. Top Marking

Figure 13. CMT2218B top marking

Table14. CMT2218B top marking description

| Marking method | Laser                                                                                                           |

|----------------|-----------------------------------------------------------------------------------------------------------------|

| Pin 1 mark     | Circle diameter = 0.3 mm                                                                                        |

| Font size      | 0.5 mm, right aligned.                                                                                          |

| Line 1 marking | 218B represents model CMT2218B                                                                                  |

| Line 2 marking | ①②③④ represents the internal tracking coding                                                                    |

| Line 3 marking | Date code is assigned by assembly factory. Y represents the last digit of the year. WW represents working week. |

## 11. Document Change List

Table15. DocumentChange List

| Rev. No.    | Chapter | Change Descriptions                                                                                            | Date       |

|-------------|---------|----------------------------------------------------------------------------------------------------------------|------------|

| Preliminary | All     | Preliminary version for internal verification                                                                  | 2017-08-07 |

| 0.2         | 5       | Change some descriptions                                                                                       | 2017-08-15 |

| 0.3         | All     | Change some descriptions                                                                                       | 2017-08-18 |

| 0.4         | 3       | Added ROM list                                                                                                 | 2017-09-04 |

| 0.5         | All     | Full update                                                                                                    | 2018-01-08 |

| 0.6         | 4.2.6   | Remove AN196 reference document                                                                                | 2020-09-11 |

| 0.7         | 1.4     | Change the Unit of Co-channel rejection, Adjacent channel rejection, Blocking, Image Rejection from dBc to dB. | 2023-05-19 |

| 0.8         | 1.4     | Update description mistake, delete the OOK modulation, for CMT2218B only supports for FSK modulation.          | 2023-09-12 |

### 12. Contact Information

Shenzhen Hope Microelectronics Co., Ltd.

Address: 30th floor of 8th Building, C Zone, Vanke Cloud City, Xili Sub-district, Nanshan, Shenzhen, GD, P.R. China

**Tel:** +86-755-82973805 / 4001-189-180

**Fax:** +86-755-82973550

Post Code: 518052

Sales: sales@hoperf.com

Website: www.hoperf.com

The information furnished by HOPERF is believed to be accurate and reliable. However, no responsibility is assumed for inaccuracies and specifications within this document are subject to change without notice. The material contained herein is the exclusive property of HOPERF and shall not be distributed, reproduced, or disclosed in whole or in part without prior written permission of HOPERF. HOPERF products are not authorized for use as critical components in life support devices or systems without express written approval of HOPERF. The HOPERF logo is a registered trademark of Shenzhen Hope Microelectronics Co., Ltd. All other names are the property of their respective owners.